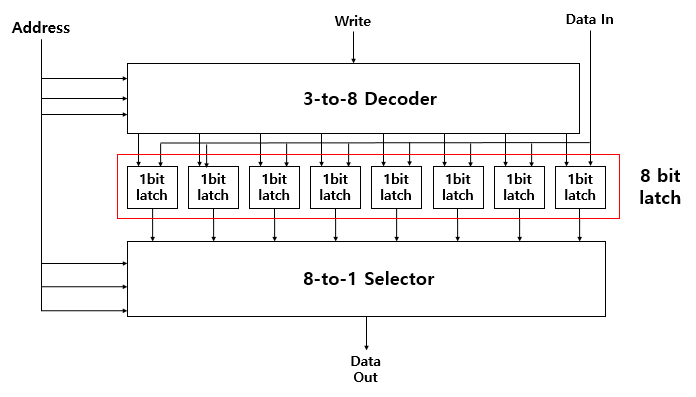

1. RAM(Random Access Memory)

- = 온전한 8 bit latch회로(=Memory)

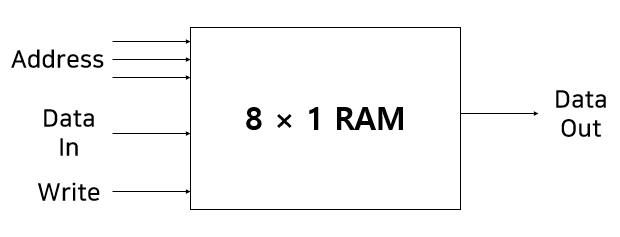

2. 8 × 1 RAM(=RAM)

- 8개 bit 중 1개의 특정 bit를 쓰고 읽을 수 있는 메모리

특징

- Memory: 데이터를 저장 가능

- Read/Write: 특정 공간에 새로운 데이터 저장, 읽기 가능

- RAM 지정을 통해 특정 공간 값 접근 가능

- 일부 메모리는 순차접근만 가능

3. RAM array

- RAM 을 여러 개를 추가했다는 의미

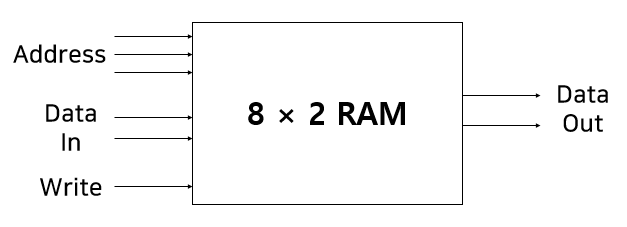

3.1. 8 × 2 RAM array

- 8 × 1 RAM은 하나의 bit만 쓰고 읽을 수 있음

- 8 × 1 RAM을 두 개 연결하면 8 * 2 RAM array가 됨

- 총 16개 중 address가 8 × 1, 8 × 1로 동시에 가리키기 때문에 두 개의 data를 한 번에 쓰고 한 번에 읽을 수 있음

- 즉, 16개의 공간 중 한 번에 2개씩 읽고 쓸 수 있기 때문에 8 × 2 RAM array

- (= 8개의 data를 읽고 쓰는데 각 데이터는 2 bits)

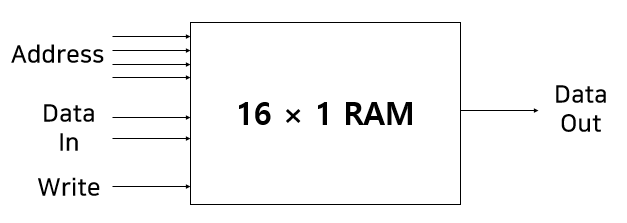

3.2. 16 × 1 RAM array

- 8 × 2 RAM array 구조에 Select, 1-to-2 Decoder, 2-to-1 selector 추가

-

- 8 * 2 RAM array 구조 위에 1-to-2 decoder 구성하며 data in은 하나

- decoder에서 2개의 data-out 중 하나를 선택해야 함

- 이 선택을 위해서는 하나의 address가 필요 -> Select

- 총 4개의 address가 필요

- 그래서 총 16개의 공간 중 하나를 선택할 수 있는 구조

-

- (= 16개의 데이터를 저장하고 읽는데, 각 데이터는 1 bit가 됨)

select

- 1-to-2 decoder에만 역할을 하는 것이 아니라 8 × 2 RAM array 아래의 2-to-1 selector에서 2개의 data-out을 받아서 둘 중 하나를 결정하는 역할

3.3. m × n RAM array

- 8 × 1 RAM을 여러 개 연결하고 여러 개의 Select로 decoder와 selector를 구성하면 많은 데이터를 읽고, 저장 가능

- 예)

- address 10이면 2^10 = 1024

- Data-in: 1byte(8bits)

- 1024 * 8 bits = 8196bits를 다루는 RAM array

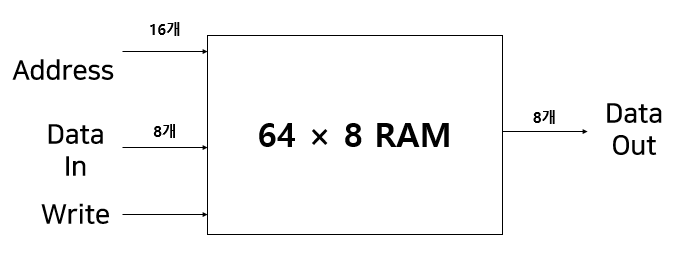

3.4. 64K RAM

- 우리나라에서는 큰의미를 가짐

- 주소가 16개(2^16) = 65536

- 데이터는 1 byte씩 = 8 bits

- 총 65536 * 8 bits를 다루는 RAM array

반응형

'CS > 컴퓨터 구조(Computer Architecture)' 카테고리의 다른 글

| [컴퓨터 구조] Program Counter(PC)란? (0) | 2023.01.07 |

|---|---|

| [컴퓨터 구조] Accumulator란? (0) | 2023.01.04 |

| [컴퓨터 구조] latch 란? (1) | 2022.12.31 |

| [컴퓨터 구조] 플립플롭이란? (0) | 2022.11.22 |

| [컴퓨터 구조] 반가산기, 전가산기, Oscillator (0) | 2022.11.11 |

![[컴퓨터 구조] RAM이란?](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fble6n7%2FbtrUEvGa5CJ%2FAAAAAAAAAAAAAAAAAAAAAC9Y12HQN7PNro6MNBCTwG73VViQs5VzGvBNKap73WqF%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1756652399%26allow_ip%3D%26allow_referer%3D%26signature%3DiC2AJdWc0DJbEXT2gt3kwn7NRT4%253D)