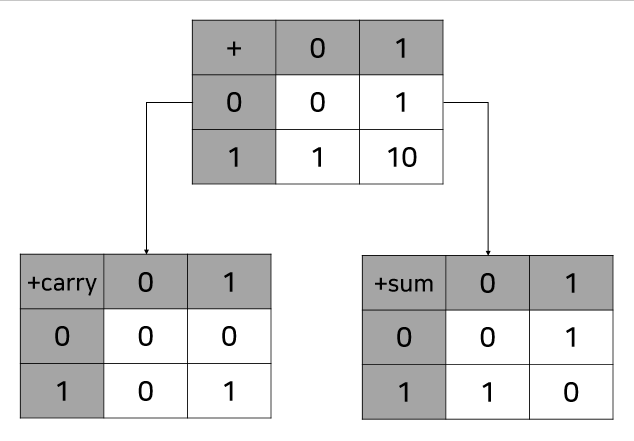

1. 가산기(adder)

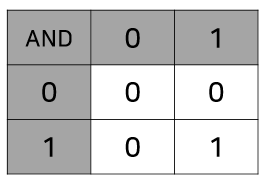

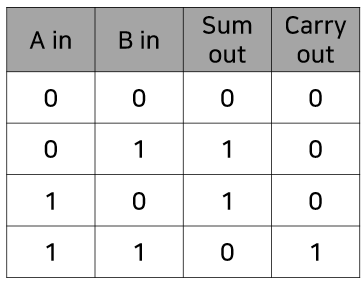

- carry bit는 둘 다 1일때만 1이고 나머지는 0으로 동작하는 논리 Gate

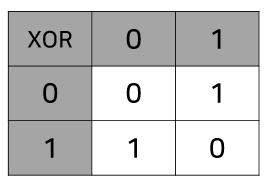

- sum bit는 둘 중 하나만 1일 때 1이고 나머지는 0으로 동작하는 논리 Gate

- sum bit와 같은 결과를 내기 위해서는 위와 같은 A와 B가 있다면, OR Output과 NAND Output 결과물을 가지고 AND Output을 통해 sum bit와 같은 결과는 낼 수 있다.

- 이러한 결과물을 XOR Gate라고 부른다.

- carry bit는 보면 결국 AND Gate이다.

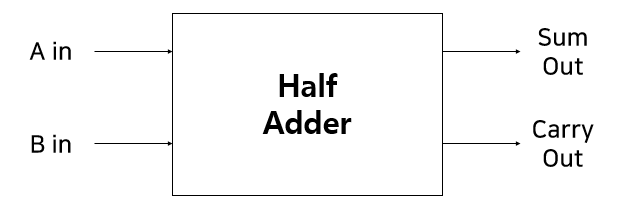

2. 반가산기(half adder)

- 두 bit를 덧셈하는 가산기

- 여기서 반가산기에 half가 붙은 이유?

- 반가산기의 반대는 전가산기이다.

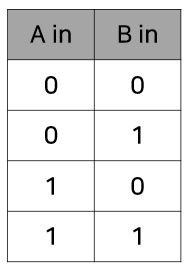

- 입력(A in, B in)이 2개이면서 출력(Carry Out, sum Out)도 2개이다.

- 현재 각각(A, B) bit자리를 더해 둘의 합 그리고 carry자리까지 출력하는 회로

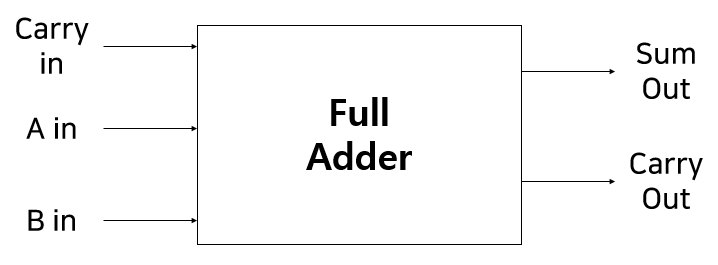

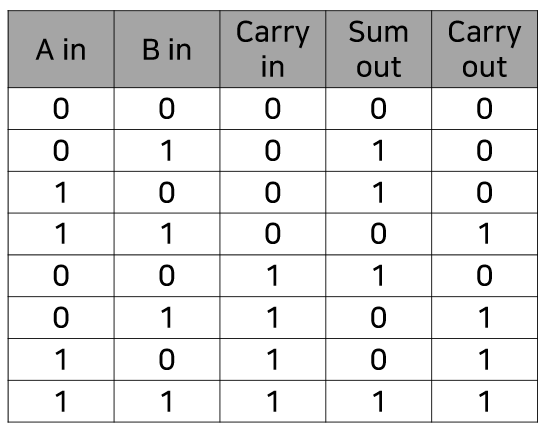

3. 전가산기(full adder)

- 두 bit외, carry까지 계산할 수 있는 가산기를 의미

- 현재 각각(A, B) bit자리를 더해 둘의 합 그리고 carry자리에서 연산결과까지 출력하는 회로

- 반가산기(half adder) 2개를 연결한 회로

- 입력(A in, B in, carry in)이 3개이면서 출력(Carry Out, sum Out)은 2개이다.

- 전가산기(full adder) 8개를 연결해서 조합하면 8비트 전가산기(8 bits full adder)가 된다.

- 총 8자리로 2진수가 표현할 수 있는 숫자는 2의 8승으로 256까지 덧셈이 가능하다.

- 8비트 전가산기 2개를 연결해서 조합하면 16비트 전가산기(16 bits full adder)가 된다.

- 여기서 2진수가 표현할 수 있는 숫자는 2의 16승으로 65536까지 덧셈이 가능하다.

- 전체적으로 뎃셈을 사용해서 곱셈이 가능하고, 덧셈의 회로를 바꾸어 뺄셈이 가능하다. 이처럼 계산하는 산술연산이 다 가능하다.

- 이에 가장 핵심이 바로 가산기(덧셈기)이다.

4. Oscillator

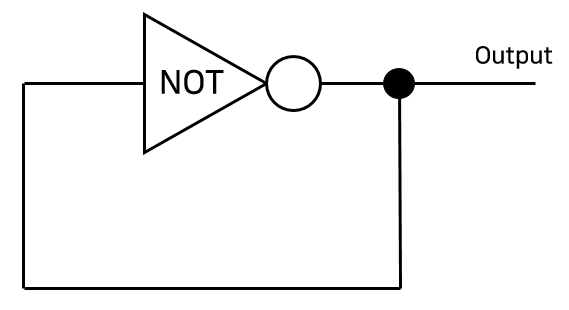

4.1. Not Gate

- input이 0이면 output은 1이다.

- 반대로 input이 1이면 output은 0이다.

- output값이 0과 1을 반복하는 회로

- CPU 전체에 일정하게 명령을 실행할 수 있도록 전원을 주었다가 일정 시간 지난 후 다시 전원을 주면서 반복.

- 전원을 받을 때마다 CPU가 모든 동작을 실행

- 일종의 클럭(Clock)이라고 하며 클럭을 만들 수 있다.

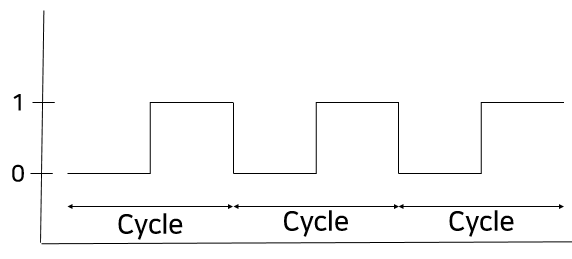

4.2. 클럭(Clock)

- 0으로 잠깐 있다가 1로 잠깐 올라가는 0과 1로 한 번씩 왔다갔다하는 시간이 일정하고 이것을 바로 1 cycle(주기)라고 한다.

- 주기: 한 사이클에 필요한 시간

- frequency(단위-hertz): 주기 / 1(cycle/sec)

- 예)

- 1 cycle이 걸리는 시간이 0.05초라면 1초에 결과적으로 20 cycle이 필요하다.

- 여기서 20 cycle을 20hertz(Hz)라고 하며 frequency라고 한다.

반응형

'CS > 컴퓨터 구조(Computer Architecture)' 카테고리의 다른 글

| [컴퓨터 구조] RAM이란? (0) | 2023.01.02 |

|---|---|

| [컴퓨터 구조] latch 란? (1) | 2022.12.31 |

| [컴퓨터 구조] 플립플롭이란? (0) | 2022.11.22 |

| [컴퓨터 구조] 비트와 논리 연산 (0) | 2022.10.28 |

| [컴퓨터 구조] 컴퓨터 구성 요소 (0) | 2022.08.08 |

![[컴퓨터 구조] 반가산기, 전가산기, Oscillator](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbhQQzB%2FbtrQYcWV5PQ%2FAAAAAAAAAAAAAAAAAAAAAAI6L49gR8IGW9sh2ME5STz6-7UfacGMjy-7_unKs_91%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1756652399%26allow_ip%3D%26allow_referer%3D%26signature%3D7kX%252FAvce03AgAL%252FwkDt7I5MVWlU%253D)